| 章节 | 内容概述 | 重点程度 |

|---|---|---|

| Ch.10 Programmable Logic 数据存储 | PLD、CPLD、FPGA 等 | 非核心 |

| Ch.11 Data Storage 数据存储 | 存储器结构和类型 | 非核心 |

| Ch.12 Signal Conversion 数据传输 | A/D, D/A, DSP | 非重点 |

| Ch.14 Data Processing 数字信号处理 | CPU、系统结构、嵌入式 |

10 数据存储

10.1 半导体存储器基础

- 位 (bit) 是最小单位;字节 (byte) 是 8 位一个单位处理数据;半字节 (nibble) 是 4 位单位;字 (word) 是位的组合,或者两个字节。

- 内存:存储的字数乘以字长。

- 地址:存储阵列横纵数据单位的位置

- 写操作和读操作:地址总线将地址码传到存储器当中,然后得到写或者读命令,将数据总线的数据传输到存储器,或者将存储器对应位置的数据传输到数据总线上。

10.2 随机访问存储器 (RAM)

- RAM:可以任意顺序读写,电源关闭的时候会丢失所存储的数据。

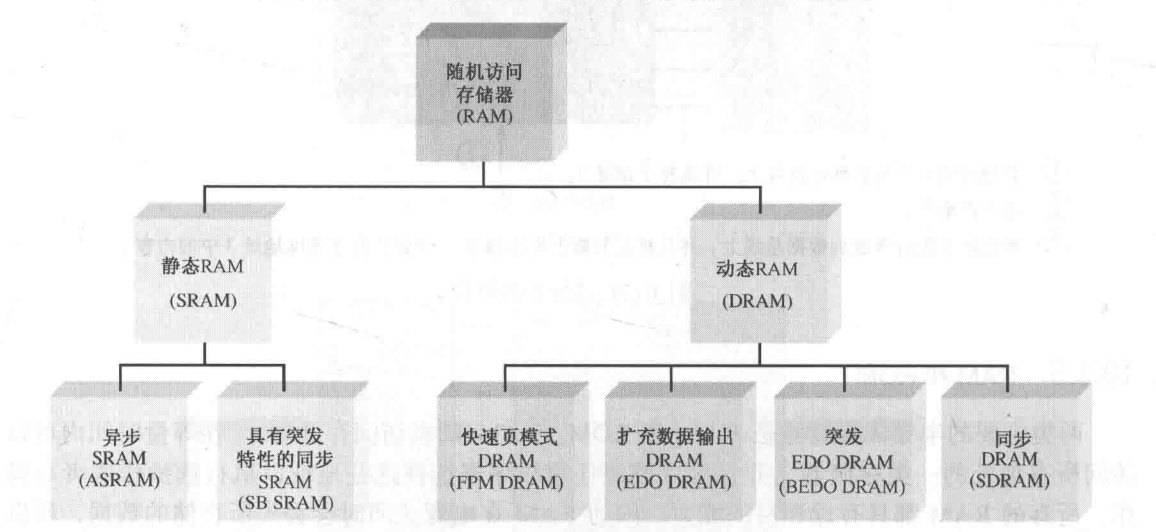

- 分类:静态 RAM (SRAM) 和动态 RAM (DRAM)

- SRAM 常用锁存器作为存储元件,只要加上直流电源就可以永远存储数据;

DRAM 常用电容作为存储元件,没有对电容再充电就不能长期存储数据。

10.3~10.4 只读存储器 (ROM)

- ROM:只有读操作,电源关闭后仍然保存数据。

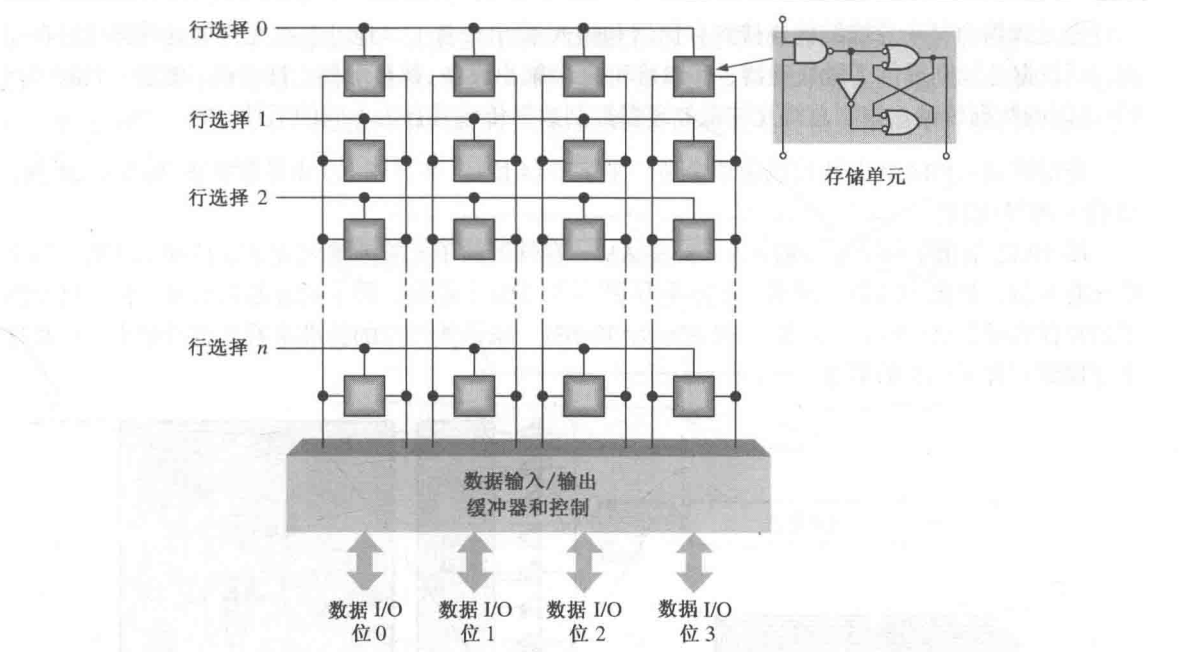

- SRAM:具有锁存器存储单元,由多个晶体管组成,输入由选择线和数据输入线连向与门实现

- 优点:速度快

- 缺点:成本高、存储密度低

- 异步 SRAM:片选 + 输入 / 输出使能,经过一定时间后,实现数据输入输出

- 具有突发特性的同步 SRAM:使用寄存器来缓冲。突发逻辑可以用单个地址对多个地址进行读写。

- 高速缓冲存储器 (Cache):常用 SRAM 构建。是一种体积小、速度快的存储器。

- 用于缓解 CPU 和主存的速度差异。它储存近期访问过的数据和指令,避免 CPU 每次都访问速度较慢的主存,可以提升系统性能。

- 层级结构:L1 Cache (CPU 内)、L2 Cache (CPU 内或外部独立芯片)、L3/L4 Cache。容量逐级增大,速度逐级变慢。

- DRAM:

- DRAM 每个存储单元由一个 MOS 晶体管 + 一个电容组成

- 优点:

- 结构简单,只需晶体管加电容

- 单位面积可以集成更多位

- 成本低

- 缺点:

- 电容会漏电,需要定期更新

- 操作电路比 SRAM 更复杂(需要专门刷新电路)

- 速度较慢(读写更加复杂)

- DRAM 的操作模式:

| 操作 | 行线 | R/W线 | DIN/DOUT | 位线动作 | 电容状态 |

|---|---|---|---|---|---|

| 写1 | 高 | 低 | DIN 高 | 电容充电 | 存1(有电) |

| 写0 | 高 | 低 | DIN 低 | 电容放电/无充电 | 存0(无电) |

| 读1 | 高 | 高 | DOUT 高 | 电容电荷传出 | 数据读出→需刷新 |

| 刷新 | 高 | 高 | DOUT 高 | 电荷重新补充 | 维持原值 |

- DRAM:每个存储单元由一个晶体管+电容组成